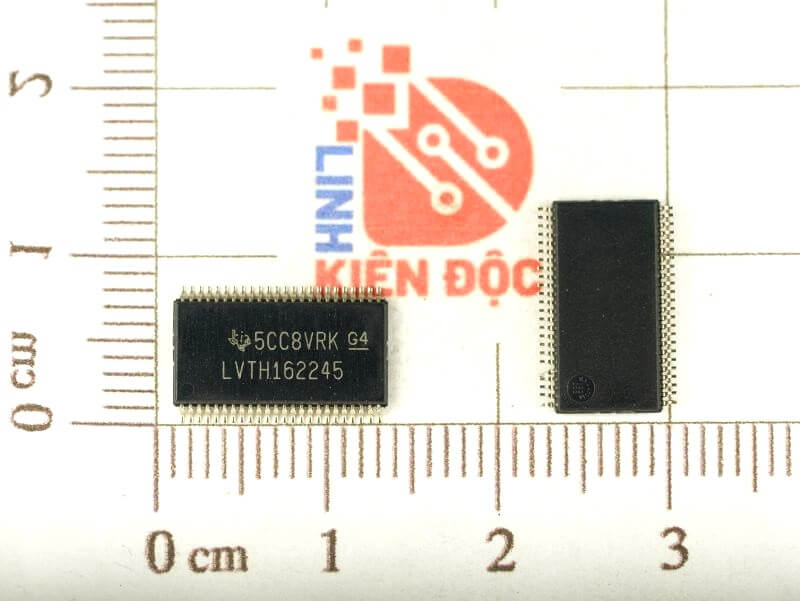

74LVTH162245DGGR, 74LVTH162245, LVTH162245 TSSOP48

30.000₫

Kinh doanh : 0973549046

Kĩ thuật viên : 0979578581

(Giờ làm việc: 8h đến 18h từ T2-T7 )

Chú ý: Chỉ gửi đơn hàng tối thiểu 50.000 vnđ

1. Giới thiệu về IC 74LVTH162245DGGR

74LVTH162245 là IC đệm bus hai chiều 16 bit (16-Bit Bus Transceiver with 3-State Outputs) thuộc dòng 74LVTH của Texas Instruments (TI).

IC được thiết kế để truyền dữ liệu hai chiều giữa hai bus song song, có điều khiển hướng truyền và cho phép ngắt ngõ ra (3-state) nhằm tránh xung đột tín hiệu.

IC hoạt động với mức logic TTL tương thích 3.3V nhưng chịu được mức 5V ở ngõ vào/ra (5V tolerant).

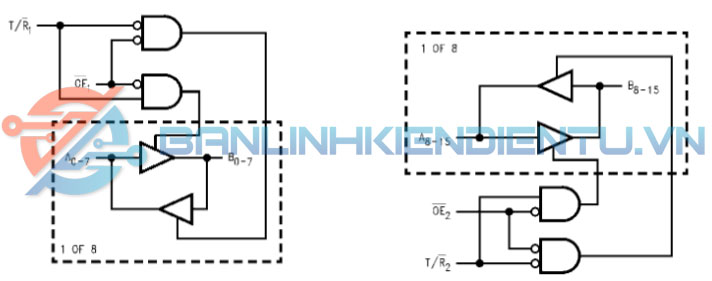

2. Cấu tạo và nguyên lý hoạt động bên trong

Bên trong IC gồm hai nhóm mạch đệm (Transceiver), mỗi nhóm 8 bit, tổng cộng 16 đường truyền song song.

Mỗi nhóm có:

-

Một chân điều khiển hướng (DIR – ký hiệu T/ R): xác định chiều truyền dữ liệu A ⇄ B.

-

Một chân cho phép ngõ ra (OE – Output Enable): điều khiển trạng thái ngõ ra (bật/tắt).

Nguyên lý cơ bản:

-

Khi DIR = High → dữ liệu truyền từ bus A → bus B.

-

Khi DIR = Low → dữ liệu truyền từ bus B → bus A.

-

Khi OE = High → tất cả ngõ ra ở trạng thái high-impedance (Z) – bus được ngắt khỏi hệ thống.

-

Khi OE = Low → bus được kết nối và truyền dữ liệu theo hướng xác định bởi DIR.

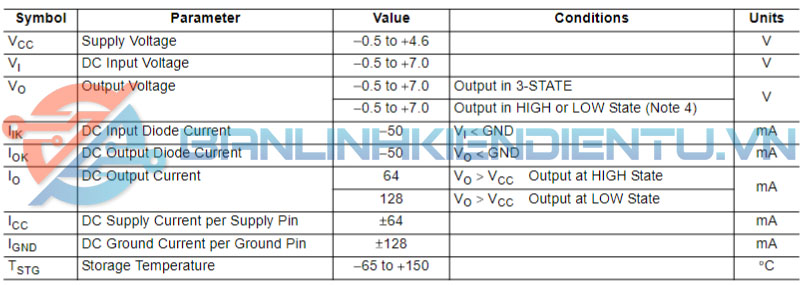

3. Thông số kỹ thuật chính của 74LVTH162245

| Thông số | Ký hiệu | Giá trị điển hình |

|---|---|---|

| Điện áp nguồn hoạt động | V<sub>CC</sub> | 3.0V – 3.6V |

| Dòng ra mỗi kênh | I<sub>O</sub> | ±64 mA |

| Mức logic tương thích | — | TTL/CMOS 5V tolerant |

| Điện áp logic “1” tối thiểu | V<sub>IH</sub> | 2.0V |

| Điện áp logic “0” tối đa | V<sub>IL</sub> | 0.8V |

| Dòng rò trạng thái Z | I<sub>OZ</sub> | ±10 µA |

| Thời gian trễ truyền | t<sub>pd</sub> | 2.0 – 4.5 ns |

| Dòng tiêu thụ | I<sub>CC</sub> | 0.5 mA (tĩnh) |

| Bảo vệ ESD | — | ±2000V (HBM) |

| Nhiệt độ hoạt động | T<sub>op</sub> | -40°C → +85°C |

| Kiểu đóng gói | — | TSSOP-48 hoặc SSOP-48 |

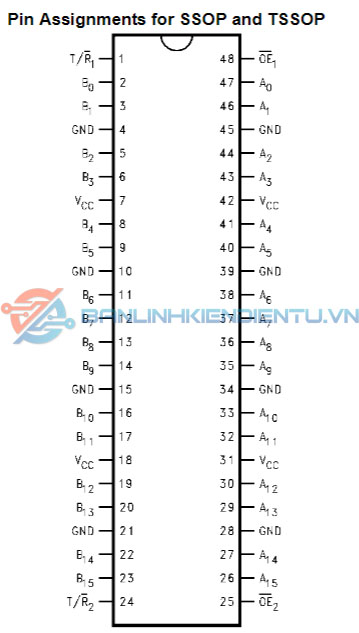

4. Kiểu chân và chức năng của 74LVTH162245DGGR (TSSOP-48)

Sơ đồ chân (Top View – TSSOP-48):

| Chân | Ký hiệu | Mô tả chức năng |

|---|---|---|

| 1 | T/R₁ | Chân điều khiển hướng truyền nhóm 1 (A0–A7, B0–B7): – High: A → B – Low: B → A |

| 2–9, 11–12 | B0–B7 | Đường dữ liệu bus B nhóm 1 |

| 10, 13, 16 | GND | Nối đất |

| 7, 18, 31, 42 | VCC | Nguồn cấp 3.3V |

| 47–40, 38–37 | A0–A7 | Đường dữ liệu bus A nhóm 1 |

| 48 | OE₁ | Cho phép ngõ ra nhóm 1 (active low) |

| 14–24 | B8–B15 | Đường dữ liệu bus B nhóm 2 |

| 25 | OE₂ | Cho phép ngõ ra nhóm 2 (active low) |

| 26–36 | A8–A15 | Đường dữ liệu bus A nhóm 2 |

| 17 | T/R₂ | Chân điều khiển hướng truyền nhóm 2 (A8–A15, B8–B15) |

| Nhiều chân GND/VCC xen kẽ | — | Dùng để giảm nhiễu và đảm bảo ổn định tín hiệu |

5. Chức năng hoạt động của 74LVTH162245

| OE (Output Enable) | DIR (T/R) | Hướng truyền dữ liệu | Trạng thái ngõ ra |

|---|---|---|---|

| Low | High | A → B | Dữ liệu từ bus A sang bus B |

| Low | Low | B → A | Dữ liệu từ bus B sang bus A |

| High | X | Ngắt (Z) | Ngõ ra ở trạng thái high-impedance |

Ghi chú:

– Hai nhóm hoạt động độc lập nhau với OE₁/T/R₁ và OE₂/T/R₂.

– Khi OE = High, bus tương ứng được ngắt khỏi hệ thống (Z-state).

6. Ứng dụng của IC 74LVTH162245

-

Kết nối bus dữ liệu 16-bit giữa CPU và bộ nhớ, vi điều khiển, FPGA.

-

Truyền dữ liệu hai chiều song song trong hệ thống vi xử lý.

-

Bộ chuyển mức logic (level translator) giữa các khối 3.3V ↔ 5V.

-

Bộ cách ly bus (Bus Buffer/Isolator) trong mạch điều khiển tốc độ cao.

-

Thiết bị truyền dữ liệu công nghiệp hoặc giao tiếp máy tính nhúng.

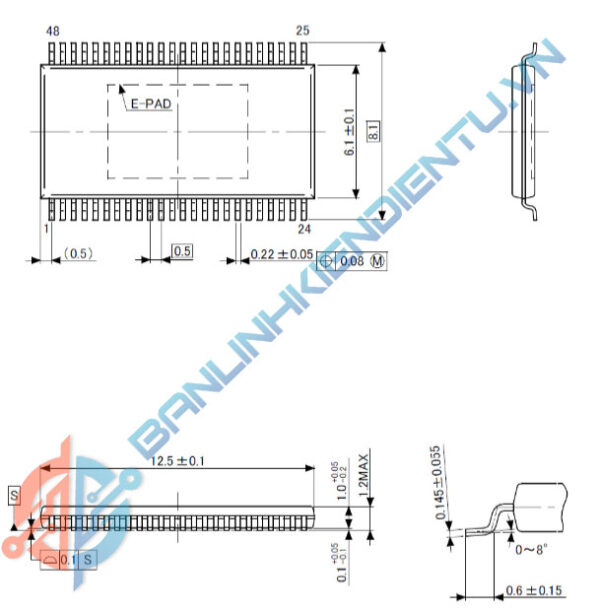

7. Kích thước vật lý của 74LVTH162245DGGR (TSSOP-48)

| Thông số | Giá trị (mm) |

|---|---|

| Chiều dài tổng | 12.9 – 13.2 |

| Chiều rộng tổng | 6.1 – 6.4 |

| Chiều cao | 1.2 – 1.6 |

| Khoảng cách chân (pitch) | 0.5 |

| Số chân | 48 |

| Kiểu vỏ | TSSOP-48 / SSOP-48 |

8. Cách đo và kiểm tra sống/chết của 74LVTH162245

A. Kiểm tra nguồn

-

Cấp 3.3V vào các chân VCC, nối GND đúng vị trí.

-

Dòng tĩnh (không tải) khoảng ≤ 1 mA.

B. Kiểm tra chức năng truyền dữ liệu

-

Kiểm tra nhóm 1:

-

OE₁ = Low, DIR₁ = High → đo tín hiệu từ A → B.

-

Cấp logic 0/1 vào A0–A7, kiểm tra đầu ra tương ứng B0–B7.

-

Đảo DIR₁ = Low → dữ liệu truyền ngược lại.

-

-

Kiểm tra nhóm 2:

-

OE₂ = Low, DIR₂ = High/Low tương tự nhóm 1.

-

-

Nếu OE = High, mọi ngõ ra phải ở mức Z (trở kháng cao) – có thể kiểm bằng đồng hồ số với chế độ đo logic high-Z (hoặc điện áp trôi tự nhiên ~nửa VCC).

C. Dấu hiệu hỏng

-

Không có thay đổi mức logic giữa A–B.

-

Có điện áp bất thường hoặc đo chập giữa VCC–GND.

-

Các ngõ ra không vào trạng thái Z khi OE = High.